[サムスン電子、7ナノEUVに3次元積層技術の適用…業界初]

サムスン電子が業界で初めて7ナノEUV(極紫外線)システム半導体に3次元積層パッケージ技術である「X-Cube」を適用したテストチップの生産に成功したと13日、明らかにした。

これを通じて、サムスン電子は最先端EUV超微細前工程だけでなく、後工程でも先端技術の競争力を確保するようになった。 これは「半導体ビジョン2030」を達成するのに、大きな役割をするものと期待される。

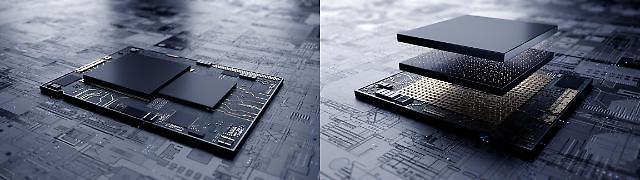

X-Cubeは全工程を終えたウェハー状態の複数のチップを上に薄く積層し、一つの半導体に作る技術だ。

システム半導体は一般的にCPU・GPU・NPUなどの役割をするロジック部分とキャッシュメモリーの役割をするSRAM部分を一つのチップに平面に並んで配置して設計する。

X-Cube技術はロジックとSRAMを単独で設計・生産して上に積層するため、全体チップの面積を減らし、高容量メモリーソリューションを装着できるため、顧客の設計自由度を高めることができる。

また、シリコン貫通電極(TSV)技術を通じて、システム半導体のデータ処理速度を画期的に向上させることができ、電力効率も高めることができる。 TSVはワイヤを利用してチップを連結する代わりに、チップに微細な穴を開け、上段チップと下段チップを電極で連結するパッケージング技術である。

このほかにも上下チップのデータ通信チャンネルを顧客の設計によって自由自在に拡張でき、信号伝送経路も最小化でき、データ処理速度を極大化できるという長所がある。

この技術はスーパーコンピューター・人工知能・5Gなど高性能のシステム半導体を要求する分野はもちろん、スマートフォンとウェアラブル機器の競争力を高めることのできる重要技術として活用されるものと予想される。

グローバルファブレス顧客はサムスン電子が提供するX-Cube設計方法論と設計ツールを活用し、EUV技術基盤の5、7ナノ工程チップの開発をすぐに始めることができる。

特にすでに検証されているサムスン電子の量産インフラを利用できるため、開発エラーを素早く確認し、チップの開発期間を減らすことができる。

亜洲日報の記事等を無断で複製、公衆送信 、翻案、配布することは禁じられています。