["ファウンドリ超格差"サムスン電子、高性能の半導体パッケージングソリューション「H-Cube」開発]

サムスン電子が半導体後工程(パッケージング)技術の革新を通じ、高性能の半導体向け2.5次元(2.5D)パッケージングソリューション「H-Cube(Hybrid-Substrate Cube)」を開発した。

サムスン電子は従来の2.5次元パッケージングソリューション「I-Cube」に続き、今回に高帯域幅メモリー(HBM)半導体を6つ以上搭載可能な業界最高仕様のH-Cubeを確保したと11日、明らかにした。

データセンター・人工知能(AI)・ネットワークなど応用先別の市場に適した適合型半導体を顧客のニーズに合わせて様々な形のパッケージで提供できるようになった。

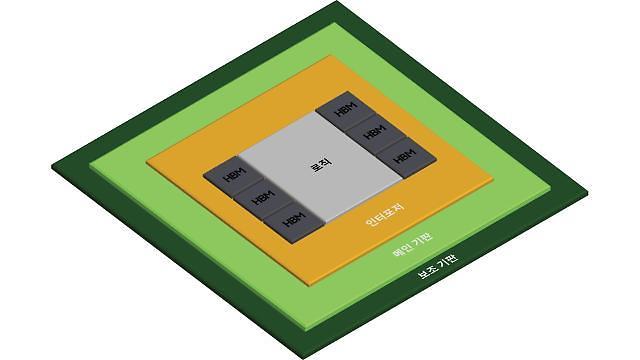

H-Cubeはロジック半導体1つと6つの高帯域幅メモリー半導体を1つのパッケージで具現した独自的な2.5次元パッケージ技術だ。様々な半導体を一つの空間に合わせ、一つの半導体チップのように運営できるようにするのだ。

2.5次元パッケージング技術はシリコン貫通電極(TSV・Through Silicon Via)を通じ、チップとチップを垂直で連結する技術である。従来の印刷回路基板(PCB)を通じてチップを連結する方式より、はるかに高い密度の連結性を具現することができる。

H-Cubeはハイスペックな特性の具現が容易なメイン基板の下に対面的の具現が可能な補助基板を追加で使用する2段ハイブリッドパッケージング構造だ。ロジック半導体と共に高帯域幅メモリー半導体を6つ以上効率的に搭載可能な長所がある。

サムスン電子はメイン基板と補助基板を電気的に連結す「Solder ball」の間隔を従来比35%縮め、基板の大きさを最小化し、多数の高帯域幅メモリーの搭載によって、増加する大面積基板製作の困難を克服した。

さらに、多数のロジック半導体と高帯域幅メモリー半導体を積層しながらも、チップに安定的な電源を供給し、信号の損失や歪みを最小化できるように、チップ分析技術も適用し、今回のソリューションの信頼度を高めた。

亜洲日報の記事等を無断で複製、公衆送信 、翻案、配布することは禁じられています。